C波段宽带捷变频率综合器设计

打开文本图片集

摘要:本文介绍了一种C波段宽带捷变频率综合器的设计方法,采用直接数字频率合成器(DDS)实现频率捷变,采用倍频链路扩展输出带宽,通过与锁相环(PLL)合成产生的本振信号混频将输出频率搬移到c波段。论述了DDS时钟电路、倍频链路以及混频部分的设计方法,并给出了达到的主要技术指标和测试结果。本文网络版地址:http:∥.cn/article/263364 htm

关键词:频率合成;频率捷变;DDS;PLL;杂散

DOI:10.3969/j.issn.1005-5517.2014.9.008

引言

频率合成器是现代通讯系统必不可少的关键电路,是电子系统的主要信号源,是决定电子系统性能的关键设备。随着系统对频率源的频率稳定度、频谱纯度、频率范围和输出频率个数的要求越来越高,高稳定、低相位噪声、低杂散,小步进和高速变频是频率合成器发展的主要趋势。

当前主流的频率合成方法分为锁相环频率合成(PLL)和直接数字合成(DDS)两种。其中锁相环电路输出频率高.相位噪声好,其缺点是频率分辨率低,频率跳变时间较长。而DDS有极好的频率分辨率,高速的频率切换时间,很好的相位噪声,但它输出频率较低,杂散信号较多。

1 频率合成方案的分析

本课题的研究背景来源于某接收机项目,为收发模块提供C波段中一定范围内小步进快速连续可变的跳频源信号。

由于DDS芯片具有频率步进小,切换迅速的特点,成为捷变频率综合器的必然选择。但是目前DDS芯片的直接输出频率无法到达C波段、需通过一定的频率合成方案实现,目前基于DDS技术的频率合成方案主要有以下3种。

1.1 DDS直接激励PLL方案

DDS的输出作为锁相环电路的基准频率,PLL电路锁相信频得到输出频率。利用DDS的高分辨率实现小的频率步进来改变参考频率,同时PLL的带通特性也能抑制部分DDS的输出杂散。

这种方法具有高频率分辨率和低杂散的优点。不过不足的是频率的切换时间由锁相环的环路滤波器的带宽决定,频率切换速度不够快。

1.2 DDS+PLL环外混频合成方案

直接数字合成产生的信号,通过与锁相环PLL环外混频将DDS输出的频谱搬移到较高的频段。

这种方法保留了DDS频率分辨率高和频率切换速度快的优点,同时将输出频率扩展到更高频段,PLL只产生固定频点、相位噪声低。其缺点是:1、DDS产生的近端杂散会通过混频过程而搬移到输出频段内,较难滤除。混频器的引入也可能产生其他非线性杂散。2、DDs的直接输出频谱只是相当于发生了搬移,输出频率的带宽仍然等于DDS的直接输出带宽,DDS直接输出带宽相对较窄,该方法不能扩展频段,当所需输出带宽超过DDs输出带宽范围时无法利用该方法实现。

1.3 DDS+倍频频率合成方案

直接将DDS的输出频率倍频到更高的频点、利用倍频链路来将DDS的输出频率倍频到所需输出频率,同时也能扩展DDS的输出带宽。

该方案能输出较多频点,获得较高的频率转换时间以及较宽的输出频带。但这种方法也存在其缺点:DDS直接倍频的过程可能会将DDS自身的杂散信号放大,同时倍频器也会产生各次谐波,需要在倍频链路中设计滤波器组来有效抑制输出杂散,该方案电路较复杂,调试起来较麻烦。

2 系统要求以及C波段捷变频率合成器的实现

系统要求频率合成器能够快速切换频率,频率步进小,杂散指标良好,要求分别产生4路输出频率信号6.5125~6.7375GHz、6.5875~6.8125GHz、6.6625~6.8875GHz、6.7375~6.9625GHz,杂散抑制优于50dBc。

根据频率合成器指标,输出带宽大于200MHz,虽然DDs直接输出带宽大于200MHz,但考虑到DDs在宽频带输出时杂散特性不好,选择DDS输出中杂散指标较好的一段使用,再通过倍频来扩展输出带宽。

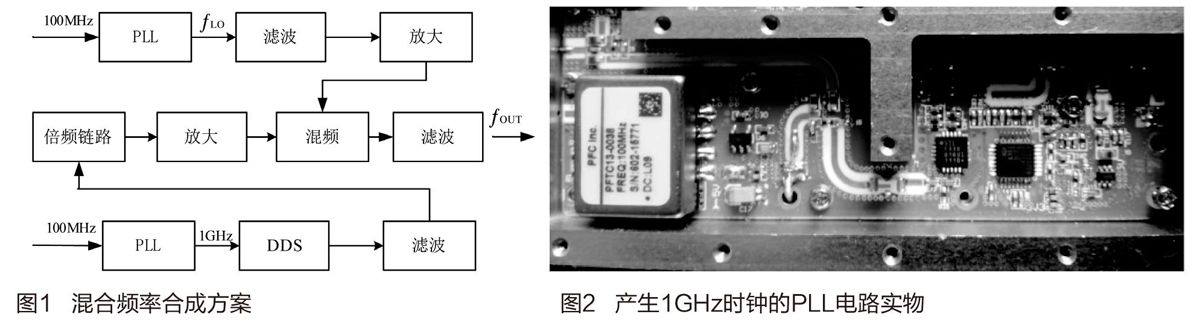

系统所需求的输出频率要求达到6.SGHz以上,如果直接通过DDS倍频达到所需频率,则需要倍频的倍数相对较高,对应倍频链路的设计较为复杂,难以保证输出信号的频谱纯度。综合考虑,选择采用DDS+倍频技术+上变频技术以便得到所需要的宽带捷变频率信号。DDS倍频输出后再与锁相环产生的较高频点的本振进行混频得到最终的输出频率信号,系统框图如图1所示。

2.1 DDS信号输出

本文采用ADI公司的高性能DDS芯片AD9858。DDS芯片AD9858具有频率转换时间短,输出频带宽的优点,能够满足对低相位噪声、低杂散噪声、快速频率切换以及宽带线性扫描的要求。参考AD985 8产品手册并结合系统要求输出频段考虑,本设计中采用AD98 5 8输出128.125MHz~183.375MHz频段,该段频谱杂散指标较小,经过4倍频后能达到系统输出的带宽。

DDS输出信号的质量取决于参考时钟信号的性能。从追求频率合成器的性能角度,应选用高性能的晶振通过倍频产生DDS时钟。但考虑到晶振倍频电路较复杂且本系统对频率合成器的相位噪声指标没有过高的要求,AD9858的时钟信号通过锁相环电路锁定输出1GHz产生,如图2所示。锁相环电路采用ADF4351芯片,该芯片集成了VCO和PLL,其基准时钟由100MHz高稳定度晶体振荡器提供,环路滤波器由ADIsimPLL软件进行仿真设计。

DDS通过单片机控制,PLL产生的1GHz作为工作时钟信号,输出信号频率128.125MHz~183.375MHz。为了抑制DDS输出的杂散,在其输出后加入6阶反切比雪夫模型的低通滤波器,经过调试后带内平坦度较好,输出经过放大器以及π衰来调节功率后进入后端倍频链路。

2.2 DDS倍频链路

D D s输出信号范围128.125MHz~183.375MHz,经过2次的二倍频产生512.5~737.5MHz的信号。为保证输出信号的杂散指标,每次倍频后需通过带通滤波器滤除基波和谐波信号。此外由于倍频器采用的倍频器均为无源倍频器,存在较大倍频损耗,所以每次倍频后需要通过放大器将信号功率放大。信号通过放大器也会产生谐波,所以在每级放大器也应设计滤波器滤除谐波保证杂散指标。

二倍频器采用AMK-2-13+,其输入频率范围为10MHz~500MHz,输出频率为20MHz~1000MHz,变频损耗为11.4dB。第一级倍频时,对基波128.125MHz~183.375MHz抑制度为43dBc左右,对三次谐波的抑制度为59dBc,对四次谐波的抑制度为15dBc左右。通过反切比雪夫模型搭建的带通滤波器对其谐波进行进一步抑制,出来的信号再通过放大器和π衰调节功率后,滤波进入下一级倍频。第二级倍频时,AMK-2-13+对基波256.25MHz~366.75MHz抑制度为36dBc,对其三次谐波的抑制度为47dBc,对其四次谐波的抑制度为16dBc。倍频后信号采用Mini公司的滤波器芯片进行滤波,再通过放大器调节功率。

2.3 混频本振信号的产生

本设计PLL产生的4个点频源分别是6.0GHz、6.075GHz、6.15GHz、6.225GHz,用作最后上变频的本振信号。4个锁相环电路均采用ADI公司的ADF41 08锁相环芯片,使用ADIsimPLL软件对锁相环路中的环路滤波器进行仿真设计。VCO选择Hittite公司的HMC358MS8G芯片,其输出功率+11dBm,相噪-110dBc/Hz@100kHz。

2.4 混频输出

DDs倍频后输出的信号分别进入混频器与PLL产生的四个固定频点本振进行上变频。混频器采用基于GaAs工艺的双平衡混频器HMC220MS8,其中频工作范围为Dc~4GHz,本振在5GHz~10GHz内时变频损耗为7dB,它本振到射频的隔离度为25dB,本振到中频的隔离度为28dB,输入1dB压缩点为8dBm左右。经过上变频后需要通过带通滤波器将混频产生的各项谐波以及泄露到射频段的本振信号滤除。带通滤波器选择采用定制的腔体滤波器,因其性能稳定可靠,带内幅频特性平坦,插入损耗小,带外抑制度高,可用于较大功率,能更好地滤除带外干扰信号,保证最终的频率输出低杂散。

3 实物图以及测试结果

本设计实物电路采用微波多层印制板电路结构,合理布局,将4路混频输出端分别布在了四个边角上,最大限度地减少了输出信号间的相互串扰。在整块电路板上采用多点,大面积就近接地,以避免地线上形成干扰。PCB板上每个引脚出都加了去耦电容以加强电路的抗噪性能。

实现的胜能指标如下:

输出频段:6.5125~6.7375GHz、65875~6.8125GHz,6.6625~6.8875GHz,6.7375~6.962GHz

频率步进:1Hz

跳频速度:≤100ns

杂散抑制:≤-58dBc

以PLL产生本振为6.075GHz时为例,该路最终应输出6.5875~6.8125GHz频率,用频谱仪测量该路最终混频输出的频谱如图5所不。

该路输出频段内最大杂散点如图6所示,此时杂散抑制为-60dBc左右。

4 结束语

本文采用DDS结合倍频和上变频技术的方案实现了C波段宽带捷变频率综合器,该频率合成器具有频率切换速度快,步进小,工作频带宽,输出杂散低等特点,具有较高的工程应用价值。

参考文献:

[1]高玉良现代频率合成与控制技术[M].北京:航空工业出版社,2002

[2]张大鹤,纪学军,李青平小步进捷变频率合成器设计技术[J].无线电工程.200g.39(6):43-46

[3]李昂.X波段连续波雷达收发前端的设计与实现[D].成都:电子科技大学.2013

[4]陈之光,陶骏,田野,等.某型高杂散抑制捷变频率合成器研制[J].压电与声光,2013,35(1):132-135

[5]李军.X波段微波倍频器的研制与一种频率源的设计[D].成都:电子科技大学.2004

版权声明:

1.文驰范文网的资料来自互联网以及用户的投稿,用于非商业性学习目的免费阅览。

2.《C波段宽带捷变频率综合器设计》一文的著作权归原作者所有,仅供学习参考,转载或引用时请保留版权信息。

3.如果本网所转载内容不慎侵犯了您的权益,请联系我们,我们将会及时删除。